1 공 웨이퍼 제작

본격적인 웨이퍼를 가공하는 전공정에 들어가기 위한 첫 단계

Silicon Ingot을 제작하고 이를 dicing한 후에 Fab에 공급

Wafer는 주로 모래에서 추출한 규소(Silicon)으로 제작되며

Ingot은 규소를 고온으로 녹인 용액에 결정핵을 넣어 빙글빙글 돌리며 결정을 성장시킨다

공 웨이퍼는 일본기업이 글로벌 60%의 시장점유율

국내에서는 SK실트론(비상장)이 있다

SK실트론은 300mm분야에서 글로벌 4위

공 웨이퍼가 Fab에 투입되어 완성되기까지 약 1개월 소요

따라서 웨이퍼의 직경을 증가시키면 한 사이클에서 생산되는 칩의 수는 증가되어 생산성이 향상

현재 많이 사용되는 300mm(12인치) Wafer는 200mm(8인치)에 비해 2.5배, 150mm(6인치)에 비해 약 4배 생산성 향상

Wafer 크기를 확대하면 Fab의 주요 설비를 교체해야 하기 때문에 막대한 투자가 필요하지만

Wafer당 생산성 향상을 위해 삼성전자, 하이닉스, IBM, Intel 등이 450mm Wafer 전화 기술 개발에 들어간 상태

2. 마스크 제작

Mask는 반도체를 개발 및 생산하기 위한 일종의 원판 필름을 만드는 과정

Fabless로부터 받은 회로설계의 패턴을 확대해 Quarz라고 불리는 합성석영유리 기판위에 전자 빔(E-Beam)을 이용해 새기면 Mask

완성

최근 미세화공정에 따른 DPT, QPT, ArF광원 사용 비중 확대로 Mask의 고사양화가 진행

Blank Mask업체

① 주로 일본업체로부터 Quarz를 수입해 금속박막필름을 증착 (sputter)

② 그 위에 감광액(PR)을 도포해서 Blank Mask 생산

③ 이를 Photo Mask업체에게 공급

Photo Mask업체가 최종적으로 패턴을 형성

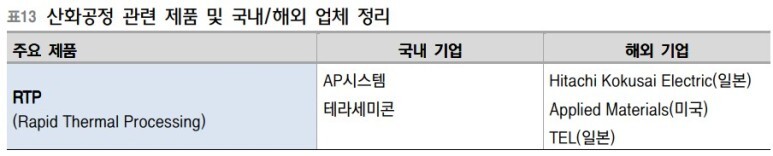

3. 산화공정 (Oxidation)

연마가 된 Wafer는 전기를 통하지 않는 상태

이를 반도체 성질을 갖게 하기 위한 첫번째 단계가 산화공정

고온(800-1000℃)에서 산소나 수증기 등을 Wafer 표면에 뿌려 실리콘산화막(SiO₂)을 형성하는 단계

산화막은 오염물질을 차단하는 역할을 하거나 Wafer에 새겨지는 회로를 보호해주는 절연막 역할을 하기도 함

산화막 형성에는 주로 고온 열처리 (RTP, Rapid Thermal Process) 방법이 쓰임

Fab 공정 장비 시장에서 2-3% 차지

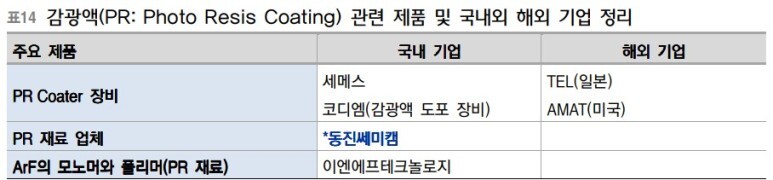

4. 감광액 도포 (Photo Resist Coating)

노광공정을 진행하기 위한 전단계

Wafer 위에 빛에 반응하는 민감한 물질인 감광액을 도포

사진을 현상하는 것과 같이 Wafer를 인화지로 만들어주는 작업

장비로는 PR Coater, Wafer 위로 감광액을 떨어뜨리고 고속으로 회전시켜 감광막을 도포하는 장비

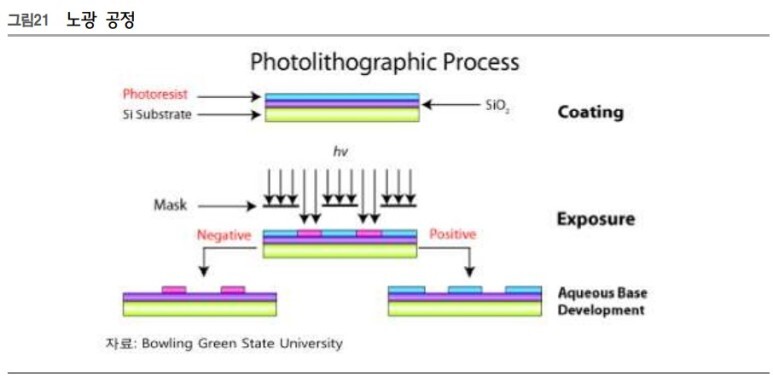

5. 노광 공정 (Exposure)

감광막이 형성된 웨이퍼를 노광장치(Stepper)에 고정하고 패턴이 새겨진 마스크를 대고 빛에 노출시키면 현상과정을 거쳐 감광막에 패턴이 생성

즉, 회로 설계를 통해 얻어진 도면을 1cm 정도의 작은 칩에 옮기는 것

전체 공정에 소요되는 시간 중 약 60%가 노광공정에 할애되며 생산원가의 약 33-37%를 차지

노광공정을 통한 원가절감 및 공정 단순화는 반도체 생산업체들의 공동 목표

반도체 미세공정화가 진행되면서 노광장비의 해상력을 높임으로써 설계상의 선폭을 최소화하는 방향으로 광원개발이 이루어지고 있음

회로와 회로사이의 간격이 줄어들어 칩 면적이 감소하면 웨이퍼 한 장에서 얻을수 있는 칩 수가 증가되고 이로인해 원가 절감 효과

더욱 미세한 회로 패턴을 구현하기 위해서는 빛의 파장이 핵심

파장이 줄어들수록 해상도가 높아져 미세한 회로 패텬을 형성할 수 있기 때문

노광 광원의 종류에는 빛의 파장 크기에 따라 KrF(불화크립톤), ArF(불화아르곤), 그리고 ArF Immersion (이머전 액침 불화아르곤) 등

13.5nm 파장의 극자외선을 이용하는 기술을 EUV (Extreme Ultra Violet)라고 하는데

현재 EUV 장비 제작 기술을 선도하는 업체는 네덜란드의 ASML로 독보적

EUV는 짧은 파장으로 해상도가 극대화되며 적은 횟수의 패터닝으로 구현 가능하기 때문에 공정수가 대폭 감소되는 장점

그러나 EUV 장비의 가격은 기존 ArF 장비의 약 2배 가격이고, 산소나 이산화탄소와 같은 물질에 흡수되는 성질이 있어 추가 보완 장치가 필요하다는 단점

현재 삼성전자는 193nm 파장인 ArF Immersion 장비를 통해 노광공정을 반복하는 DPT(Double Patterning Technology), QPT(Quardraple Patterning Technology) 방식을 채택

DPT는 첫번째 공정에서 회로 형성 후, 두번째 공정에서 회로 사이에 또 다른 패터늘 추가하는 방식

가존 ArF장비를 활용해 구현 가능하며, 현재 기술로는 EUV방식보다 가격 대비 생산효율이 좋음

그러나 멀티패터닝으로 인해 공정이 미세화될수록 원가 상승을 초래하고 생산 효율이 하락할 여지

기존공정 : 증착1 → 노광1 → 식각 1

DPT : 증착1 → 노광1 → 식각1→ 증착2 → 식각2

QPT : 증착1 → 노광1 → 식각1→ 증착2 → 식각2 → 증착3 → 식각3

Check Point : 미세화공정, QPT 확대 vs EUV 장비 적용

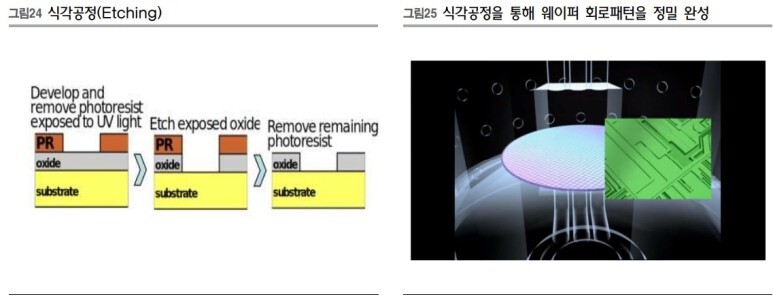

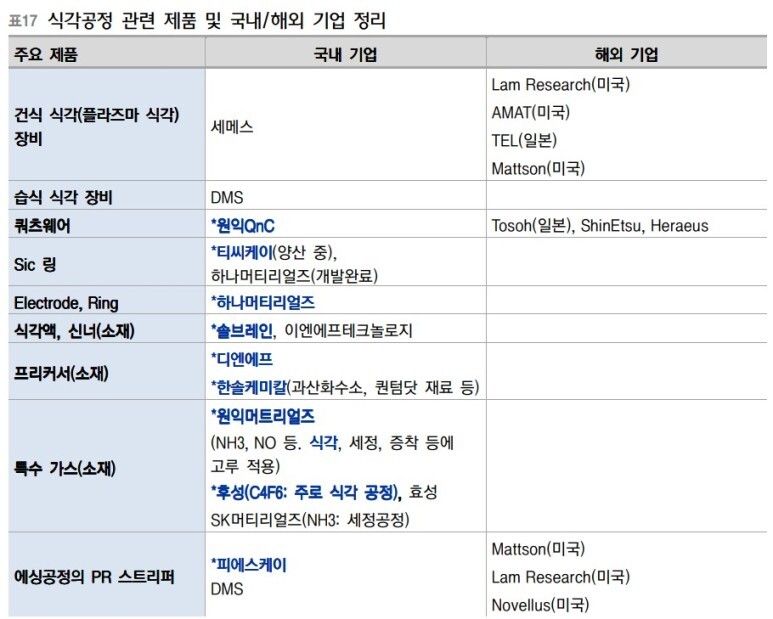

6. 식각공정 (Etching) / 애싱공정 (Ashing)

식각공정은 웨이퍼에 그려진 회로패턴을 정밀하게 완성하는 공정

노광공정을 거친 웨이퍼에서 불필요한 부분의 박막을 물리적/화학적 방법을 이용해 선택적으로 제거

이때 액상 또는 기체 형태의 부식액(Etchant)를 활용해 불필요한 부분을 선택적으로 제거함으로써 웨이퍼에 마스크와 동일한 패턴을 만들어 낸다

포토공정을 거친 웨이퍼에 부식액을 뿌리면 감광액에 의해 덮여있는 산화막 부분은 부식액에 아무런 영향을 받지않고 노출된 산화막만 부식액에 의해 녹게됨

그후에 Ashing공정을 통해 감광액을 제거하면 결국 감광액에 의해 보호받는 부분의 산화막만 남아있고 감광액에 의해 보호받지 못한 부분은 제거되어 마스크 패턴대로 산화막 패턴이 웨이퍼 위에 형성

회로 패턴공정이 반복되는 만큼 식각공정도 증가

식각에는

- 습식 (Wet Etching) : 용액 사용

- 건식 (Dry Etching) : 반응성 기체 사용

습색 대비 건식의 가격이 더 높으나,

미세와공정이 가속화되어 회로선폭이 좁아지고 있어 습식보다 더 정밀한 건식 식각 형태가 확대

건식식각은 플라즈마식각으로도 불리는데

진공챔버에 가스를 주입해 전기에너지를 공급해 플라즈마상태를 만든 후

웨이퍼 표면에 감광액(PR)이 도포되지 않는 면을 제거하는 방법

플라즈마가 반응기체(Radical)로 이루어져 웨어퍼 표면에서 목표물과 화학작용을 일으켜 식각.

반응기체란 전기적으로 중성이지만 불완전한 화학적 결합을 하고 있어 다른 물질과 매우 잘 반응하는 성질을 가진 입자

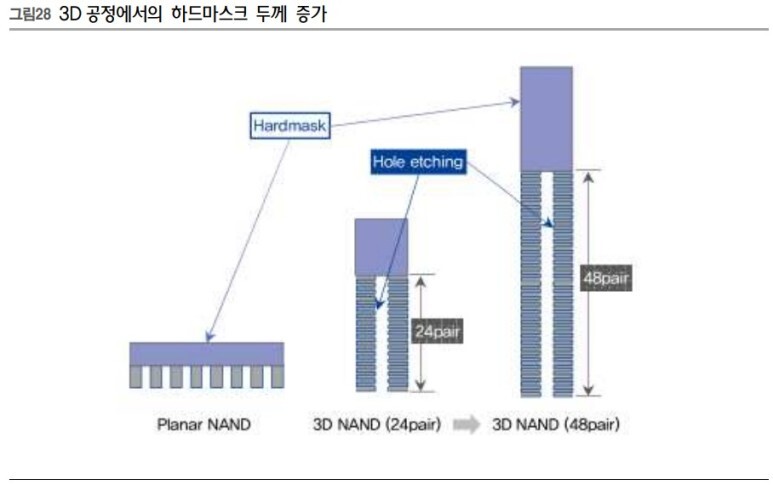

특히 3D NAND로 가면 적층수 증가에 따른 Dry Etching에 대한 수요가 증가하고 있는데

3D NAND에서 Dry Etching Gas로 주로 쓰이는 물질은 CF계열 가스

하드마스크 증착공정 추가

미세화공종이 심화되고 적층화 정도가 높아지면서 식각하게되는 홀이 더욱 깊고 얇아져야 함

이때 나타나난 문제점은 스캐너의 파장이 짧아지면서 초점심도(Depth of Focus)가 낮아지게 되는데

이로인해 감광액(PR)의 두께가 얇아지게 된다는 점

이러한 PR을 보완하기 위해 탄소가 혼합된 ACL(Amorphous Carbon Layer)이 사용

ACL은 SiO, Poly-Si 등의 박막재료와 식각 선택비가 높기 때문

ACL을 증착하는 장비가 PECVD ACL이고, 국내에서는 테스가 PECVD ACL 장비를 공급

Check Point : 깊고 넓은 식각

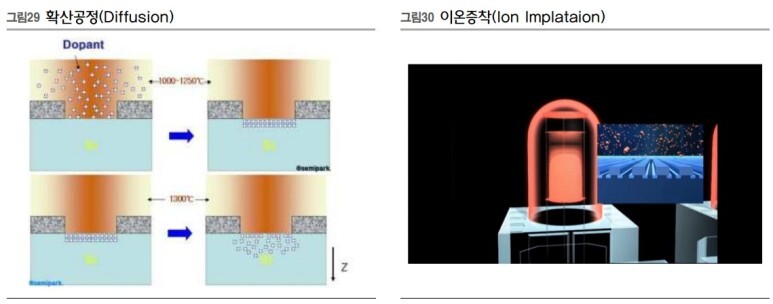

7. 이온 증착 (Ion Implatation) / 확산공정 (Diffusion)

확산공정은 식각 공정 이후 웨이퍼에 Dopant(반도체에 첨가되는 미세한 불순무례을 주입해 반도체 소자형성을 위한 특정 영역을 만드는 역할 수행

이때 도핑되는 원자들의 제어 정확성을 위해 이온 형태의 불순물 (인, 붕소 등)을 주입해 전자소재의 영역을 만들어 주는 이온 증착과정을 거치기도 한다.

또한 이때 일정한 소자형성을 위해 어닐링(Annealing)이 필요하다

확산공정에서는 가스간 화학반응을 통해 형성된 물질을 웨이퍼 표면에 증착함으로써 여러가지 막을 형성하게 된다

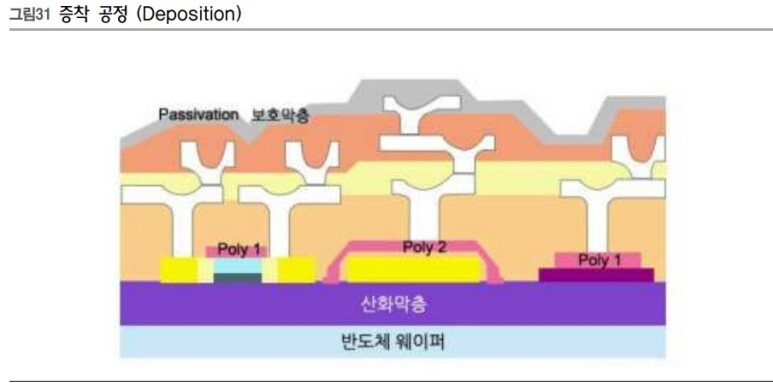

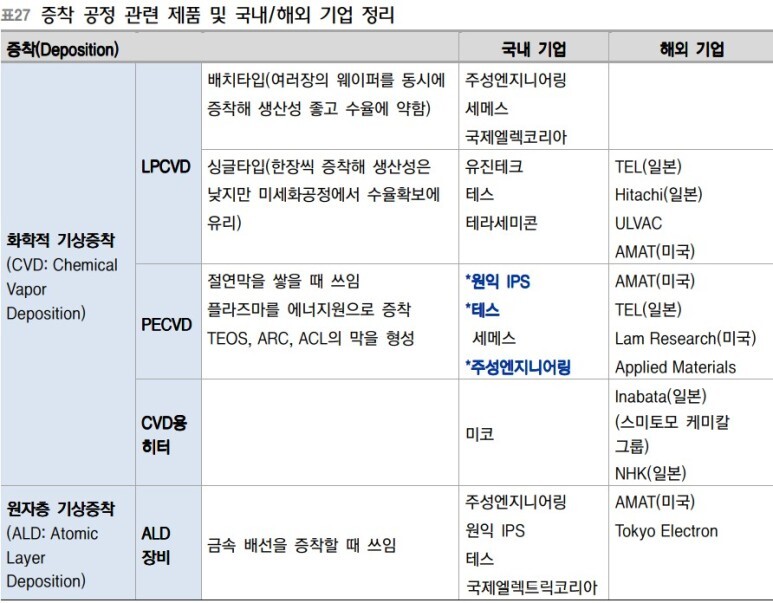

8. 증착공정 (Deposition)

증착공정은 얇은 막을 입히는 도금기술

진공챔버속에서 금속이나 화학물을 가열/증발시켜 그 증기를 물페 표면에 박막으로 입히는 공정

이렇게 박막을 입히는 이유는 반도체 소자들을 서로 연결시켜주시 위해서

대규모 집적회로를 웨이퍼 위에 만들기 위해서는 1개 층으로 보죽호기 때문에 여러 층을 쌓아 올려야 함

이러한 구조를 만들기 위해 웨이퍼 위헤 박막을 입히고 노광 및 식각 공정을 반복

이렇게 증착공정을 통해 반도체 소자들을 서로 연결시키는 박막이 형성되면

웨이퍼 상 회로사이의 전기적 신호를 이어주는 도적막과

전기적으로 분리시켜주는 절역막 기능을 수행

증착장비시장은 Fab공정 장비의 22% 비중 차지

주요 증착장비는

- 화학적 기상증착 (CVD, Chemical Vapor Deposition)

- 원자층 증착 (ALD, Atomic Layer Deposition)

화학적 기상증착에는 압력, 온도에 따라 LPCVD, PECVD 등으로 다시 분류

반도체공정에서는 막 두께의 균일도를 조절할 수 있고 대량 생산 가능한 PECVD(플라즈마 CVD)가 가장 많이 사용

PECVD는 플라즈마를 에너지 원으로 증착하는 것으로, Thermal 방식에 상대적으로 저온 상태에서 공정처리가 가능하기 때문에 빠른 증착이 가능하고 또한 온도에 약한 금속막 증착에도 용이

PECVD장비는 주로 절연막을 쌓을 때 쓰이고, ALD 장비의 경우는 금속 배선을 증착할 때 주로 쓰임

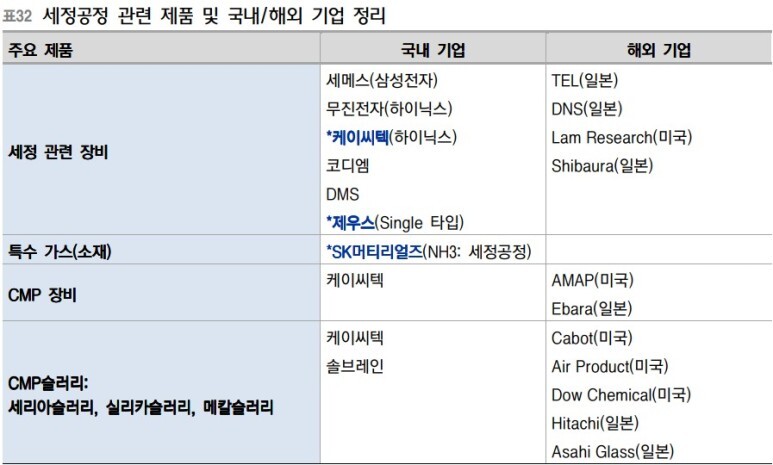

9. 세정공정 (Cleaning) / 화학기계적 연마 공정 (CMP)

세정공정은 반도체 제조 공정 중 발생하는 각종 오염원들을 화학 용액을 사용해 방지하고 제거함으로써 반도체의 전기적, 물리적 특성을 향상

CMP공정은 우수한 품질의 웨이퍼 양산을 위해 웨이퍼 표면을 기계적, 화학적으로 평평하게 만들어주는 공정

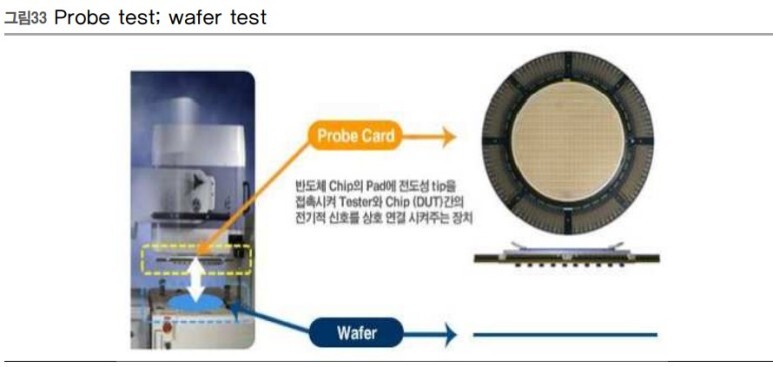

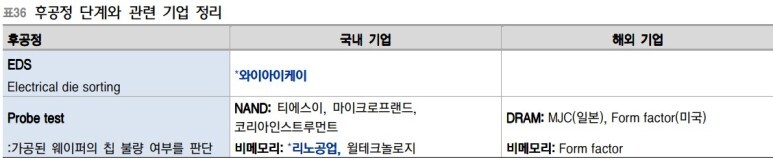

양품선별 공정, EDS 공정 및 Probe Test

EDS (Electrical Die Sorting) : 전기적 특성을 통해 웨이퍼 상에 있는 칩(Die)들이 원하는 품질에 도달했는지 체크하는 공정

Wafer Test라고 불리는 Probe Card는 전기적 신호를 이용하여 반도체의 불량 여부를 검사하는 부품

PCB위에 미세한 핀을 심어 칩의 본딩 패드와 1:1로 접속시키면서 테스트 장비를 통해 검사

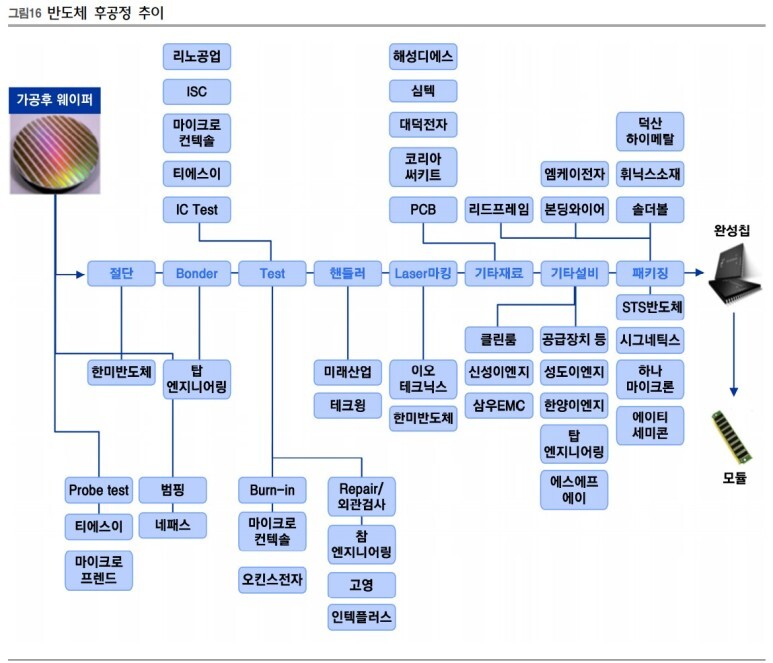

후공정

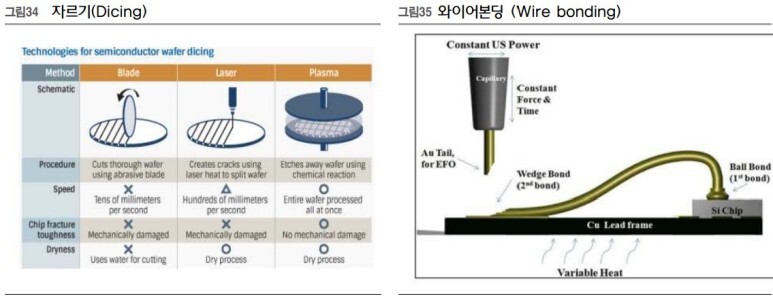

절단 (Dicing)

뤠이퍼를 조각을 잘라냄

다이아몬드로 된 톱이나 레이저 광선 사용

웨이퍼는 동그란 모양이 가장 효율이 좋고

절단에는 사각형 패턴이 Dead Space가 적어 가장 효율이 좋다

Die Attach

Die를 Lead Frame이나 PCB(Printed Circuit Board) 기판위에 옯기는 작업

Lead Frame은 구리 등을 주원료로 만든 금속기판으로

- Die와 외부회로를 연결시켜 주는 전선(Lead) 역할과

- 반도체 패키지를 전자회로 기판에 고정시켜 주는 버팀대(Frame) 역할을 동시에 수행

Lead Frame이 좁은 면적에 많은 수의 Lead를 정밀하게 만들수록 기술 수준이 높다

Wire Bonding

칩 마운트 공정에서 기판 위에 올려진 Die의 접점과 기판의 접점을 가는 금선을 사용해 연결하는 공정

빠른 속도를 필요로 하는 반도체 칩의 경우에는 전선에서 일어나는 신호 지연 현상을 줄이기 위해 전선 대신 다시 표면에 직접 전극이 되는 Bump(돌기)를 형성하고 기판에 직접 실장한다. 이러한 패키징 방식을 Flip Chip이라고 함

Flip Chip은 Die 표면에 솔더 볼 등의 돌기를 형성하고 패드 부분이 기판과 마주보게 한 후 직접 융착하는 방식

신호처리가 빠르고 접점도 여러개 만들수 있다는 장점

TSMC는 FoWLP(Fan-out Wafer Level Packaging)이라는 첨단 패키팅 기술 도입

팬아웃은 웨이퍼는 형성하는 Bump, 즉 입출력(I/O) 단자를 칩 안과 바깥쪽 모두에 배치시키는 기술

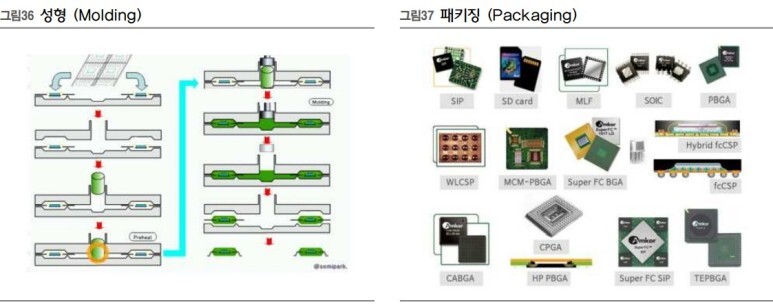

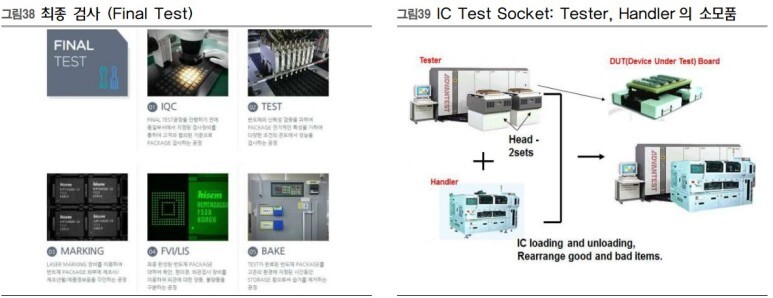

성형(Molding) / Laser Marking / Packaging

성형은 반도체를 밀봉하는 과정

연결부위 보호를 위해 화학수지로 밀봉

그 이후 제품명 등을 새기면 하나의 반도체 단품 칩이 완성

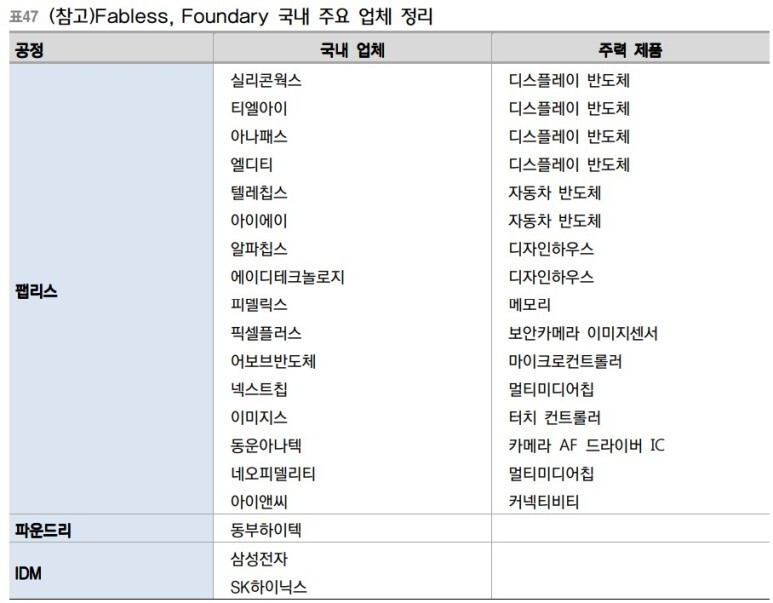

후공정 Test

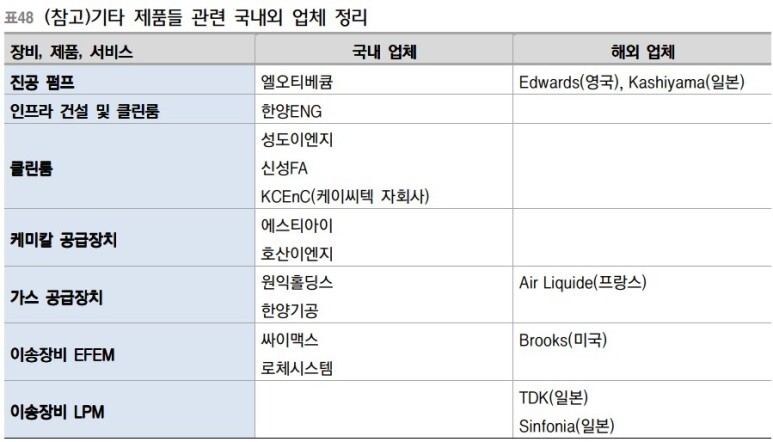

IC Test Socket

IC Test 소켓은 반도체 후공정 패키징 단계에서 전기적 신호로 불량여 부 테스트

IC test 소켓의 생산 방식은 크게 Pin type과 Silicon type이 있으며

대표적인 기업으로는

- Pin type에 리노공업이 있고

- Silicon type에는 ISC가 있다.

Burnin Socket을 생산하는 마이크로컨텍솔과 NAND Probe Card를 생산하는 티에스이도 Silicon type test 소켓 시장으로 진출했다.

Pin type은 R&D, 비메모리 등에 강점이 있 고,

Silicon type은 메모리, 대량생산을 진행하는 Chip에 강점이 있다.

Burn-In Test Socket

번인테스트는 스트레스 테스트(가혹한 환경에서 Test)

컴퓨터, 모바일 등의 장시간 가동시 발생하는 열적 조건을 조성하여 보통 섭씨 125도 정도의 온도조건에서 4 ~ 48시간 동안 Cell에 Data를 쓰고 지우며 각각 Cell의 동작여부를 검사하는 것

번인테스트의 경우 메모리 반도체를 중심으로 적용

'Investment > Stock' 카테고리의 다른 글

| 다우의 개 전략 (0) | 2022.01.09 |

|---|---|

| 연금투자자의 ETF 테마 (0) | 2022.01.09 |

| 강방천 인터뷰 (0) | 2021.06.13 |

| 주식회사 대한민국 서프라이즈 (0) | 2021.06.08 |

| KOSPI 고배당 50 (0) | 2021.06.08 |